AD9552是一款小数N分频、基于锁相环(PLL)的时钟发生器,专为取代高频晶体振荡器和谐振器而设计

产品详情

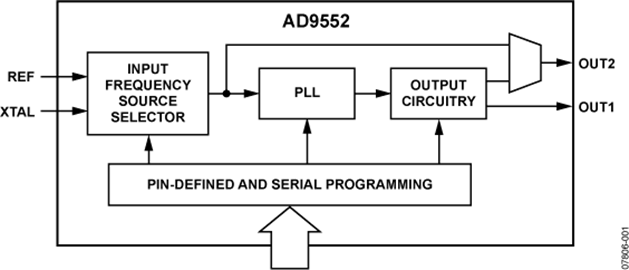

AD9552是一款小数N分频、基于锁相环(PLL)的时钟发生器,专为取代高频晶体振荡器和谐振器而设计。该器件采用Σ-Δ调制器(SDM)来处理小数频率合成。用户将单端时钟信号直接与REF引脚相连,或者在XTAL引脚上连接一个晶体谐振器,即可提供输入参考信号。

AD9552为引脚可编程器件,根据8种常用输入频率的其中一种频率,可提供64种标准输出频率中的一种频率。该器件还有一个三线式SPI接口,用户可以通过该接口自定义设置输入与输出频率比。

AD9552需用外部电容来构成PLL的环路滤波器。虽然AD9552严格按照CMOS工艺制造,但其输出与LVPECL、LVDS或单端CMOS逻辑电平兼容。

额定工作温度范围为−40°C至+85°C工业温度范围。

应用

- 高频VCXO、OCXO和SAW谐振器的高性价比替代产品

- 极其灵活的频率转换,低抖动,适合SONET/SDH(包括FEC)、10-Gb以太网、光纤通道和DRFI/DOCSIS

- 高清视频频率转换

- 无线基础设施

- 测试与测量(包括手持式设备)

优势和特点

- 将低频输入参考信号转换为高频输出信号

- 输入频率范围:6.6 MHz至125 MHz

- 输出频率最高达900 MHz

- 预设引脚可编程频率转换比

- 通过SPI端口设置任意频率转换比

- 片内VCO

- 晶体谐振器和/或外部振荡器可作为基准频率源

- 欲了解更多特性,请参考数据手册

本文来源网友上传,不代表hdxin.com蝴蝶芯城立场,如有侵权或其他问题,请及时联系我们举报

热门资讯

- MAX32670是一款超低功耗、高性价比、高可靠性的32位微控制器,在实现复杂的传感器处理设计的同时不会影响电池寿命

- MAX32550嵌入式安全方案采用多重先进的物理安全机制保护敏感数据,提供最高等级的密钥存储安全保护

- MAX28200是一款低功耗、16位MAXQ®微控制器(µC),设计用于智能电话和消费类电子等低功耗应用

- DS5003安全微处理器集成了最先进的加密功能,包括一套专门设计的安全机构,能够抵御各种级别的威胁,包括监测、分析和物理攻击

- ADUCM331集成了所有在各种工作条件下对12 V电池参数(如电池电流、电压和温度)进行精确智能监控、处理和诊断等必需的功能

- ADUCM350是一款可配置的阻抗转换器和恒电位仪,具有电流和电压测量功能,适合电化学传感器和生物传感器

- ADA4558 是用于桥式传感器的完全集成的传感器信号调节器 IC

- ADUCM320具有低功耗ARM Cortex-M3处理器和一个32位RISC机器,峰值性能最高可达100 MIPS

- ADUCM363自带一个片内32 kHz振荡器和一个内部16 MHz高频振荡器

- ADUCM3027微控制器单元(MCU)均为集成电源管理的超低功耗微控制器系统,可用于处理、控制和连接